全部

1049

1049

0

0

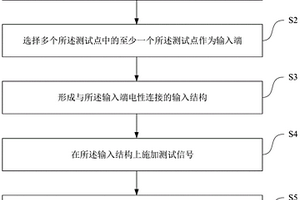

本发明提供了一种半导体器件失效分析方法,包括如下步骤:暴露出半导体器件的测试区域,所述测试区域包括多个测试点;选择多个所述测试点中的至少一个所述测试点作为输入端;形成与所述输入端电性连接的输入结构;在所述输入结构上施加测试信号;使用电性测试探针扫描测试除施加了测试信号的所述输入端之外的其他所述测试点。本发明通过引入一种新的半导体器件失效分析方法,在使用导电原子力显微镜等电性探针测试方法对半导体器件进行测试分析时,形成与测试点电性连接的输入结构,通过输入结构准确地对测试点施加偏压,并通过多个输入结构有效地缩减了失效分析所需的人力和时间成本。

1226

1226

0

0

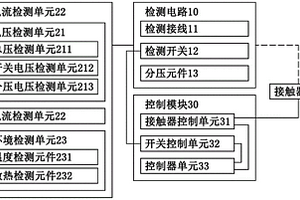

本发明提供一触器失效检测方法和接触器失效检测系统,其中所述接触器失效检测系统包括一检测电路、一检测模块以及一控制模块,所述检测电路电气连接于所述电池模块和所述接触器,以形成一检测回路,其中所述检测模块被电气连接于所述检测电路,由所述检测模块检测流经所述接触器的电流和对应所述接触器的分压,以得到所述接触器的接触电阻的阻值,其中所述控制模块被电气连接于所述检测电路和所述检测模块,所述检测模块根据所述检测模块检测的数据信息计算所述接触器的温升,并根据所述接触器的实时温度判断所述接触器的有效性。

927

927

0

0

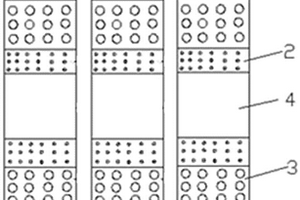

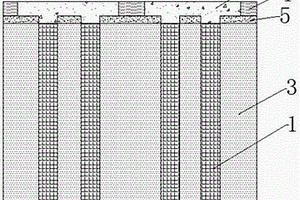

本发明公开的一种半导体结构的失效分析方法包括:提供一待测半导体结构,待测半导体结构包括衬底、栅极结构、介质层、互连金属层和钝化层,且衬底内形成有阱区、源漏极;去除钝化层、互连金属层、介质层以及栅极结构以将源漏极的上表面予以暴露;继续将源漏极上表面暴露的待测半导体结构放入氢氟酸混合溶液中浸泡以对该待测半导体结构进行染色操作;观察进行染色操作后的待测半导体结构以对该待测半导体结构进行失效分析;通过该方法不需要对每一个晶体管进行电特性分析的精确定位,而只需要定位出一个小于10um×10um的区域,即可快速确认芯片的失效是否由LDD未有效注入引起,从而降低了失效分析的难度以及失效分析的成本。

1033

1033

0

0

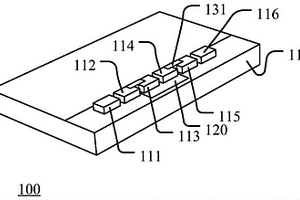

公开了一种失效分析方法及结构,方法包括:获取测试结构的位置以及与所述测试结构对应的目标焊盘的位置;将所述目标焊盘电连接至空白焊盘上;通过所述空白焊盘对所述测试结构进行失效分析,其中,所述目标焊盘位于所述测试结构上方,将所述目标焊盘电连接至所述空白焊盘上后,所述目标焊盘与所述空白焊盘之间实现电交流。该申请中通过将目标焊盘与空白焊盘电连接,通过在空白焊盘扎针进行失效分析的方法,避免了直接在目标焊盘扎针进行失效分析的过程中,多次扎针引起的测试结构损伤的情况,提高了失效点定位的准确性。

844

844

0

0

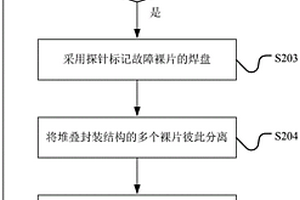

本申请公开了一种堆叠封装结构的失效分析方法及结构,所述堆叠封装结构包括堆叠且粘接在一起的多个裸片,所述多个裸片各自包括裸露的焊盘。所述失效分析方法包括:对所述堆叠封装结构进行电测量,以确认故障裸片;采用探针标记所述故障裸片的焊盘;将所述堆叠封装结构的多个裸片彼此分离;以及对已经标记的所述故障裸片进行失效分析。该失效分析方法从堆叠封装结构中定位和标记故障裸片,在堆叠封装结构的多个裸片分离之后能够快速的找到故障裸片,进一步定位故障裸片的内部位置,因而不仅降低了测试成本,而且提高了效率。

864

864

0

0

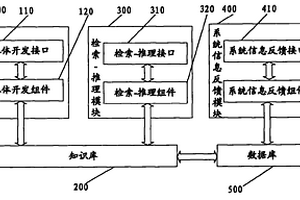

本发明公开了一种失效模式分析知识管理系统,包括知识库和检索-推理模块。所述知识库用于预设与产品质量特性关联的失效模式分析信息和与所述失效模式分析信息对应的预防措施信息。所述检索-推理模块用于接收客户端系统发送的失效模式分析知识检索-推理请求,并根据所述检索-推理请求对所述知识库的失效模式分析信息和预防措施信息进行检索和推理,获取所述检索和推理的反馈结果,并将所述反馈结果发送给所述客户端系统。本发明失效模式分析知识管理系统实现了失效模式分析知识的及时传递,也能为相关人员提供决策支持。本发明同时公开了一种失效模式分析知识管理方法。

964

964

0

0

本发明涉及半导体器件检测领域,尤其涉及一种半导体器件失效分析方法。在该半导体器件失效分析方法中,将插销和金属层间的介电质层全部刻蚀掉,再观测插销与金属层间连接部分,观测其中异常情况,找到导致产品失效的根源,方便实用。

1034

1034

0

0

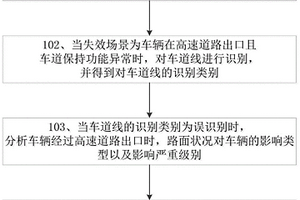

本申请实施例公开了一种车道保持功能失效分析方法、系统、电子设备及存储介质,方法包括:检测车道保持功能的失效场景;当失效场景为车辆在高速路出口且车道保持功能异常时,对车道线进行识别,并得到对车道线的识别类别;当车道线的识别类别为误识别时,分析车辆经过高速路出口时,路面状况对车辆行驶的影响类型以及影响严重程度级别;对于其它的失效场景,分析车道保持功能异常的原因类型。本申请实施例能够根据检测到的数据自动化分析车道保持功能异常时,路面状况对车辆的影响以及严重程度级别,以及分析车道保持功能异常发生的原因,相比原始的主观判断和手动分析,节约了大量时间,且分析结果更加准确。

1008

1008

0

0

本申请一种闪存芯片位线间漏电失效分析的方法,涉及芯片失效分析领域,通过采用非破坏性分析工艺,将FIB切分工艺和奈米级探针量测工艺相结合,在完全不破坏前端工艺所有材料的状况下,直接定位出失效的栓塞处,且其可检测位于栓塞不同位置的桥连(如位于栓塞顶部、中间或其他任何位置处的桥连),并能够获得较好的TEM样品,以便于后续TEM的精准观测,即在有效提高失效分析的可靠性的同时,还能大大降低失效分析所花费的时间及工艺成本等。

1198

1198

0

0

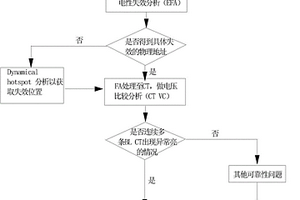

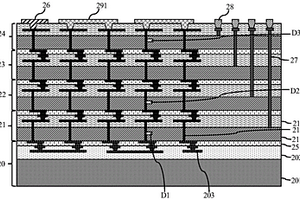

本发明涉及半导体可靠性分析领域,尤其涉及一种半导体器件失效分析的方法。本发明建立一种针对存储器的失效分析的方法,通过对失效区域及其周围区域的连接通孔进行电压对比分析并对电压对比分析结果剖析,以检测出快闪存储器由于冗余替换的存储区域缺陷经过可靠性测试或实际使用后造成的临近区域的失效问题。在可靠性失效中对冗余替换的信息进行分析,为冗余电路的替换造成的可靠性失效问题提供有力的分析依据,并对可靠性失效率的降低提供了分析及改善的方向。

1074

1074

0

0

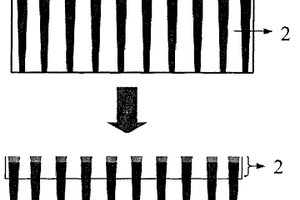

本发明提供一种存储器芯片位线失效分析方法,用以对包含埋入式位线及金属位线结构的存储器芯片进行位线失效分析,每条所述埋入式位线与相应的所述金属位线之间通过多个位线接触窗相连,所述方法包括以下步骤:去除所述存储芯片的金属位线之上的钝化层、互连金属层及层间介质层,暴露出所述金属位线;通过电测试确定存储芯片上相互之间存在短路的两条金属位线,逐段切割其中的一条金属位线,使得该金属位线中连接于相邻位线接触窗的部分之间均被割断;去除存储芯片的衬底及包含在衬底内的埋入式位线,形成检测样片;对所述检测样片进行电势对比成像观测,确定所述短路金属位线的具体失效位置。

1142

1142

0

0

本发明提供一种存储器芯片位线失效分析方法,包括以下步骤:通过机械研磨去除待分析芯片的互连金属层和位线层的大部分;通过机械研磨去除待分析芯片的衬底的大部分;通过湿法刻蚀完全去除待分析芯片的残存的衬底;通过干法刻蚀去除待分析芯片位线接触窗底部的介质层的大部分,保留一薄层的介质层;对待分析芯片的位线接触窗的顶部进行检测,确定位线失效的具体位置。本发明方法可使待分析芯片充分减薄,可直接通过电子显微镜进行观测确定其位线短路失效的具体位置,大大提高了工作效率,节省了时间成本。

1199

1199

0

0

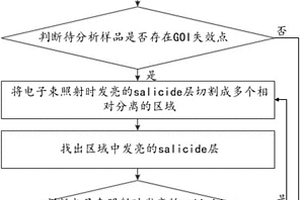

本发明涉及一种GOI失效点无损定位方法及GOI失效分析方法,包括步骤1,去除待分析样品的金属互连层,获取具有裸露salicide层的预处理待分析样品;步骤2,基于PVC法,采用电子束照射所述预处理待分析样品的salicide层,并观察其是否发亮;是,则所述待分析样品存在GOI失效点,执行步骤3;否,则所述待分析样品不存在GOI失效点,结束操作;步骤3,将电子束照射时发亮的salicide层切割成多个相对分离的区域;步骤4,再次基于PVC法,采用电子束照射所述区域,并找出所述区域中发亮的salicide层;步骤5,循环执行步骤3和步骤4,直至电子束照射时发亮的salicide层的大小不能进行切割时,结束操作。本发明实现GOI失效点的高精度定位,且整个定位过程不会导致GOI失效点的进一步破坏。

1141

1141

0

0

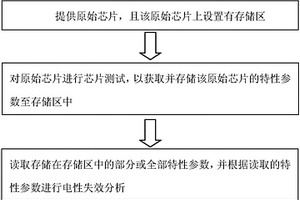

本发明涉及半导体制造技术领域,尤其涉及一种对失效芯片进行电性失效分析的方法,通过在CP测试过程中记录芯片的特性参数,在CP测试最后将收集到的芯片特性参数写入安全寄存器内,并使其变为只读状态,以便于在后续的电性失效分析中,能快速高效得到初始CP中芯片的特性参数,因此一定程度上节约人力和测试机台成本,提高后期对芯片的分析效率。

800

800

0

0

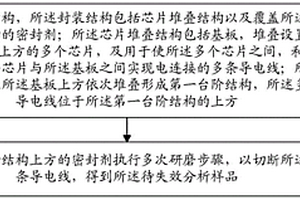

本发明实施例公开了一种待失效分析样品的制备方法,所述方法包括:提供封装结构,所述封装结构包括芯片堆叠结构以及覆盖所述芯片堆叠结构的密封剂;所述芯片堆叠结构包括基板,堆叠设置在所述基板上方的多个芯片,及用于使所述多个芯片之间,和/或所述多个芯片与所述基板之间实现电连接的多条导电线;所述多个芯片在所述基板上方依次堆叠形成第一台阶结构,所述多条导电线位于所述第一台阶结构的上方;对所述第一台阶结构上方的密封剂执行多次研磨步骤,以切断所述多条导电线,得到所述待失效分析样品。

827

827

0

0

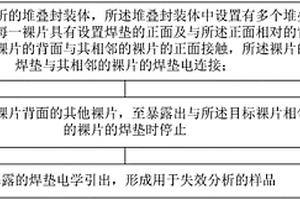

本发明提供一种失效分析样品的制备方法及失效分析样品,制备方法包括如下步骤:提供待分析的堆叠封装体,堆叠封装体中设置有多个堆叠的裸片,每一裸片具有设置焊垫的正面及与正面相对的背面,裸片的背面与其相邻的裸片的正面接触,所述裸片的焊垫与其相邻的裸片的焊垫电连接;去除目标裸片背面的其他裸片,至暴露出与所述目标裸片相邻的裸片的焊垫时停止;将暴露的焊垫电学引出,形成用于失效分析的样品。本发明优点是,对目标裸片背面进行去除操作,且利用非目标裸片焊垫作为电连接处,从而避免对目标裸片具有电路器件的正面进行去除操作,保护了正面的电路器件,能够制备出完整无损伤的目标裸片,大大提高了制样成功率,大大降低了制样难度。

1235

1235

0

0

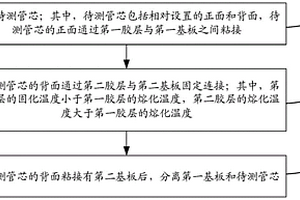

本公开实施例公开了一种失效分析样品的制作方法。所述方法包括:提供待测管芯;其中,所述待测管芯包括相对设置的正面和背面,所述待测管芯的正面通过第一胶层与第一基板之间粘接;将所述待测管芯的背面通过第二胶层与第二基板固定连接;其中,所述第二胶层的固化温度小于所述第一胶层的熔化温度,所述第二胶层的熔化温度大于所述第一胶层的熔化温度;在所述待测管芯的背面粘接有所述第二基板后,分离所述第一基板和所述待测管芯。

938

938

0

0

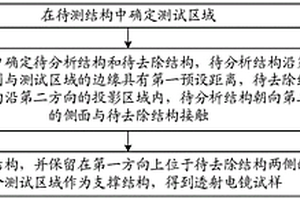

本申请实施例公开了一种透射电镜试样及其制备方法、待测结构的失效分析方法,其中,所述透射电镜试样的制备方法包括:在待测结构中确定测试区域;在测试区域中确定待分析结构和待去除结构,所述待分析结构沿第一方向的两端分别与所述测试区域的边缘具有第一预设距离,所述待去除结构位于所述待分析结构沿第二方向的投影区域内,所述待分析结构朝向所述第二方向的侧面与所述待去除结构接触,所述第一方向与所述第二方向之间的夹角大于0°且小于180°;去除所述待去除结构,并保留在第一方向上位于所述待去除结构两侧的至少部分所述测试区域作为支撑结构,得到透射电镜试样,其中,所述支撑结构与所述待分析结构形成一体成型的至少一个U型支架。

1072

1072

0

0

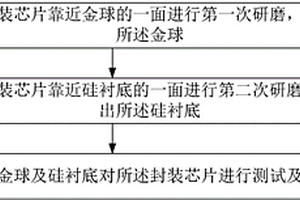

本发明提供了一种对封装芯片进行测试及失效分析的方法,对封装芯片靠近金球的一面进行第一次研磨,至暴露出所述金球,从而可以采用探测板通过金球对所述封装芯片进行探针测试;对封装芯片靠近硅衬底的一面进行第二次研磨,至暴露出所述硅衬底,从而可以采用红外定位的方法确定封装芯片的失效点,避免了现有技术中高温和化学腐蚀对封装芯片的影响或破坏,提高对封装芯片进行失效分析的准确性及效率。

894

894

0

0

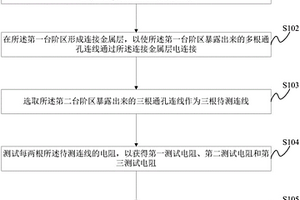

本申请公开了一种字线电阻测试方法及三维存储器失效分析方法,其中,所述字线电阻测试方法首先将三维存储器的第一台阶区和第二台阶区的多根通孔连线暴露出来,然后通过在第一台阶区形成连接金属层的方式,将多根字线通过通孔连线和连接金属层连接起来,最后通过在第二台阶区测试每两根待测连线的电阻,并根据测试获得的第一测试电阻、第二测试电阻和第三测试电阻计算三个所述待测连线的电阻,也即得到了与这三根待测连线对应的字线电阻,从而实现了对三维存储器中字线电阻的测量,为对三维存储器进行失效分析奠定了基础。

721

721

0

0

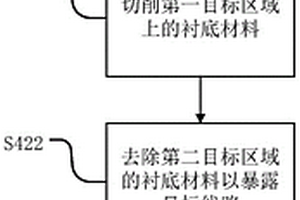

本发明公开了一种管芯失效分析方法及堆叠封装芯片失效分析方法,管芯包括衬底以及位于衬底上的器件层,失效分析方法包括:从管芯的背面,即衬底所在面,对管芯中的缺陷进行热点定位;从管芯的背面,去除衬底以暴露目标线路;以及在管芯的背面进行电测量以获得缺陷的信息。堆叠封装芯片包括引线框、堆叠于引线框上的多个管芯、以及覆盖引线框和多个管芯的封装料,失效分析方法包括:对堆叠封装芯片进行电测量以确定故障管芯;若存在未进行失效分析的故障管芯,则重复执行失效分析步骤;失效分析步骤包括:去除引线框、封装料的一部分和/或管芯,直至暴露出首个未进行失效分析的故障管芯的衬底;采用管芯失效分析方法对故障管芯进行失效分析。

1012

1012

0

0

本发明提供了一种半导体测试结构及半导体器件的失效分析方法,通过晶圆键合结构的顶部的测试焊盘和外接焊盘对至少位于所述晶圆键合结构的顶面晶圆和底面晶圆之间的每个晶圆均进行电性测试,以检测出失效的晶圆;以及,对所述失效的晶圆进行失效分析,以定位出晶圆键合结构中的失效的晶圆中的失效点,使得至少能够测试出晶圆键合结构的顶面晶圆和底面晶圆之间的晶圆是否失效以及测试出失效的晶圆中的失效点,进而使得能够快速且准确的定位多片晶圆键合的结构中的失效晶圆以及失效点,提高了失效分析的效率和成功率。

1050

1050

0

0

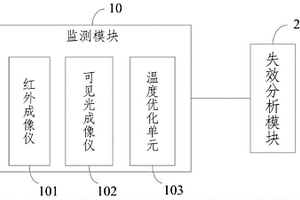

本发明提供刀具失效过程实时检测及优化数据分析系统,包括监测模块和失效分析模块;所述监测模块,用于实时获取刀具工作过程中刀具的纹理特征值和温度特征值;所述失效分析模块,用于基于已训练的刀具失效模型对所述纹理特征值和温度特征值进行处理,得到刀具失效状态。通过测试和提取刀具红外信号特征样本,断精度可达到80%以上,有效解决了刀具工作状态难以实时监测与诊断的技术难题,对提高刀具的工作效率以及节能降耗具有非常重要的意义。

中冶有色为您提供最新的湖北武汉有色金属失效分析技术理论与应用信息,涵盖发明专利、权利要求、说明书、技术领域、背景技术、实用新型内容及具体实施方式等有色技术内容。打造最具专业性的有色金属技术理论与应用平台!

2025年11月07日 ~ 09日

2025年11月07日 ~ 09日  2025年11月14日 ~ 16日

2025年11月14日 ~ 16日  2025年11月14日 ~ 16日

2025年11月14日 ~ 16日  2025年11月14日 ~ 16日

2025年11月14日 ~ 16日  2025年11月21日 ~ 23日

2025年11月21日 ~ 23日