全部

1092

1092

0

0

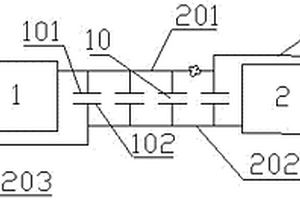

本发明一种主动测试电压对比度失效定位方法,其中,包括以下工艺步骤:步骤一,将所要测试的样品通过导电双面胶带黏贴在支撑盘上;步骤二,在支撑盘上黏贴单面隔离胶带,并使单面隔离胶带的两端接近被测样品;步骤三,在单面隔离胶带上设有多个电池,并在每两个电池之间设有垫片连接,之后在首端电池的顶面设有一单面导电胶带并黏贴在单面隔离胶带上,在末端电池的底面设有一双面导电胶带并黏贴在单面隔离胶带上;步骤四,利用引线将单面隔离胶带上的单面导电胶带与双面导电胶带远离电池的一端与被测样品的压点连接;步骤五,对被测样品进行测试。通过本发明一种主动测试电压对比度失效定位方法,能够有效地使操作检测方式变得简易,不需要操作者对其有很丰富的操作经验,使用操作成本低廉,同时能够灵活性的对测试样品进行测试。

1239

1239

0

0

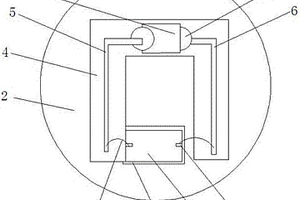

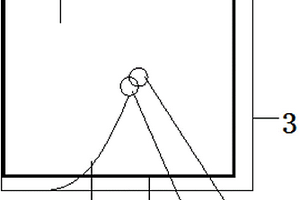

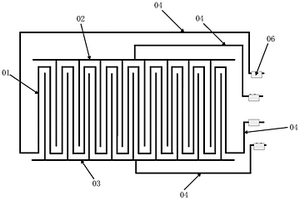

本发明公开了一种用于背面EMMI失效分析的装置,包括一PVC电路板、一信号输入输出底座;所述PVC电路板的中心设置有一透明的有机玻璃片,有机玻璃片的四周设置有多个金属引脚;PVC电路板的四个角分别设置有电路板金属衬垫;每个金属引脚分别通过金属线连接一跳线接口,每个跳线接口通过金属线分别与四个电路板金属衬垫连接;所述信号输入输出底座包括座体,座体的四个角分别设置有底座金属衬垫,底座金属衬垫的位置与所述电路板金属衬垫的位置相对应。本发明能够使背面EMMI失效分析更加简单、快速和可靠地定位到失效点,只需要花费几个小时的时间就可以完成原先需要几个工作日才能完成的失效缺陷的定位。本发明还公开了一种背面EMMI失效分析方法。

1196

1196

0

0

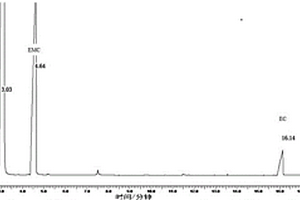

本发明涉及一种用于超级电容器失效分析的数据库及超级电容器的失效分析方法。所述用于超级电容器失效分析的数据库包括:(1)基于大量数据概括的由N个超级电容器组成电容器组中失效几率和失效原因之间的一一对应关系,N≥100;(2)超级电容器在不同使用工况下建立的性能与循环次数或性能和使用时间之间的第一函数关系;(3)超级电容器在不同荷电状态或/和不同存储时间下与其外在表观之间的第二函数关系。

1042

1042

0

0

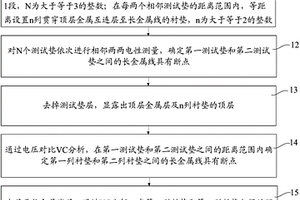

本发明公开了一种正交通孔链测试结构开路失效的分析方法,先电性验证哪条正交通孔链出现开路情况,逐层研磨至失效位置上层介质层;将开路正交通孔链一端接地,使其处于接地状态,该通孔链另一端处于悬空状态,另一条相邻正常的通孔链处于悬空状态,在失效点处上层金属互联层会出现明暗差别的电压衬度图像,观察失效点处上层金属互联层上表面是否有失效点;在确定的上层金属互联层失效点处的x方向与失效区域相似结构处,利用聚焦离子束去层直至看见下层金属互联层结构,去层区域中与失效点X方向所对应的下层金属互联层所在位置即为失效点下层金属互联层位置,从而确定TEM的制样位置。本发明能够精确定位电路中开路失效模式的异常位置。

本发明公开一种提高绝缘体击穿电压失效分析效率的测试结构,包括:若干并联电容,每一个电容的上极板均通过第一接线连接第一金属垫,每一个电容的下极板均通过第二接线连接第二金属垫,其特征在于,还包括:第三金属垫,通过第三接线连接所述第二接线;第四金属垫,通过第四接线连接所述第一接线。本发明的优点是:采用新的测试结构后,对测试结果没有影响,同时在失效分析时也能保证绝大部分样品能找到失效位置。

915

915

0

0

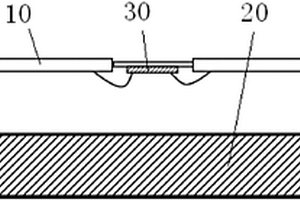

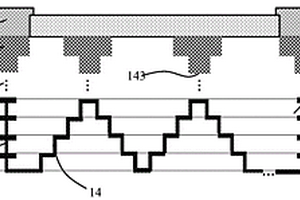

本发明公开了一种CPI测试结构,包括:基底,其中形成有层间介电层;钝化层;设置在所述基底表面;顶层金属层,设置在所述钝化层下方;层间金属层,其包括贯穿所述层间介电层的层间互连结构,所述层间互连结构设置有首端和末端,所述首端和末端分别与顶层金属层电连接;所述层间互连结构还包括多个凸出端部,所述凸出端部延伸至顶层金属层并与顶层金属层电连接。本发明可节省失效分析过程中剥掉更多金属及介电层次所花的时间,提高失效分析效率。本发明还涉及一种基于该CPI测试结构的失效分析方法。

982

982

0

0

本实用新型涉及一种带有失效分析测试金球的CSP封装件,所述CSP封装件为IC芯片,所述IC芯片包括电子元器件层、测试金球和封装层,所述电子元器件层封装在所述封装层内,所述电子元器件层具有突出在所述封装层外的锡球,所述锡球与所述电子元器件层中的电子元件相连,所述锡球与所述测试金球相连。本实用新型可以实现在对IC芯片做失效分析的时候,可以对IC芯片通电。

917

917

0

0

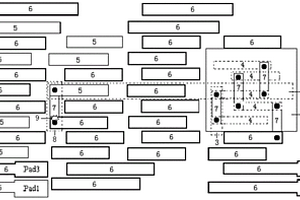

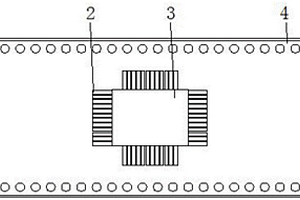

本实用新型公开了一种便于IC卡失效分析的测试板,包括芯条、测试板本体和背板,所述测试板本体的上表面开设有通槽,且测试板本体的上表面开设有安装孔,所述安装孔共设有四十八个,且四十八个安装孔每二十四个为一组,每组安装孔关于测试板本体的上表面等距分布,所述芯条焊接在测试板本体的上表面位于通槽的一侧外端面,所述芯条共设有四个,且四个芯条关于通槽的上表面呈矩形阵列分布,所述背板焊接在测试板本体的后表面,所述背板采用玻璃制成,且背板采用透明设计。本实用新型便于失效分析,节省大量时间。

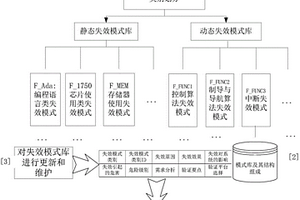

本发明提供了一种基于失效模式分析的卫星星载制导与导航软件的设计和测试方法,该测试方法包括如下步骤:S1:自n个所述第二终端获得其失效情况的反馈;若所述第一终端的数据库中未记录该失效情况对应的失效类别条目,则进入步骤S2;S2:将得到的失效类别条目归类到数据库中的失效模式类别中,并得到每个失效情况对应的失效类别条目;S3:重复步骤S1至S2,且在重复的过程中,同时进入步骤S4;S4:根据所需测试的软件的需求,索引当前数据库中相应的失效模式类别,参考该失效模式类别下失效类别条目中记载的信息设计测试用例,对卫星星载制导与导航软件在终端的运行进行测试。

856

856

0

0

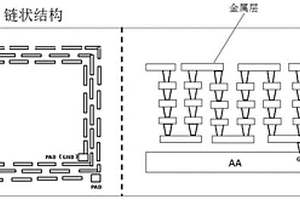

本发明公开了一种应力环失效测试结构,包括:多个金属层以及连接在各金属层之间的过孔组成的链状结构,所述链状结构环绕应力环相邻布置,所述链状结构两端形成有焊盘,所述链状结构两端焊盘其中一端焊盘接地,另一端焊盘空接。本发明还公开了一种利用所述应力环失效测试结构的应力环失效定位分析方法。本发明能通过电压衬度对比的方法定位应力环周围测试结构的断点位置,通过测试结构的断点位置判断应力环切片过程中所受应力损伤的方向,进一步指出应力环发生应力失效的位置,提高了FA失效分析的效率;并且,本发明提供的应力环失效测试结构相邻应力环对内部芯片也可起到二次保护作用。

1223

1223

0

0

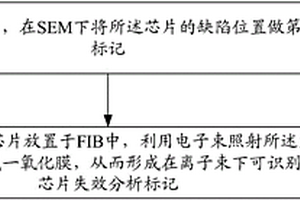

本发明揭示了一种芯片失效分析方法及芯片失效分析标记,包括:提供待测芯片,在SEM下将所述芯片的缺陷位置做第一标记;将所述待测芯片放置于FIB中,利用电子束照射所述第一标记以形成一氧化膜,从而形成在离子束下可识别的芯片失效分析标记。这避免了利用FIB离子束挖洞之前可能出现的寻找不到特征点的情况,节省了操作时间,可靠性高,并且在SEM中能够达到30nm的精度,能够满足实际需求。

1114

1114

0

0

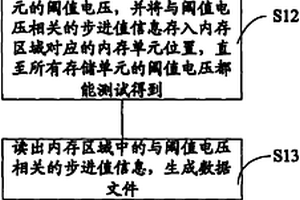

本发明提出一种存储单元失效分析的测试方法,包括:定义内存区域,所述内存区域中的内存单元与芯片上存储单元数量及位置一一对应;对存储单元进行可调数值范围内的加压,测量得到各存储单元的阈值电压,并将与阈值电压相关的步进值信息存入内存区域对应的内存单元位置,直至所有存储单元的阈值电压都能测试得到;读出内存区域中的与阈值电压相关的步进值信息,生成数据文件;对数据文件进行分析得到阈值电压对应存储单元位置的信息,同时能计算出整个存储芯片阈值电压分布的信息。本发明能很精确地进行阈值电压失效点的定位,提高了测试效率。

945

945

0

0

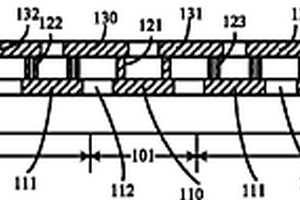

本发明提供一种用于失效分析的测试结构,包括测试单元结构且依次堆叠的第N至第N+m个半导体结构层;第N个半导体结构层的引线端部设有通孔接触点;第N+1至第N+m个半导体结构层的引线端部设有金属块,第N个半导体结构层的通孔接触点通过通孔与第N+1个半导体结构层的金属块接触;第N+1至第N+(m‑1)个半导体结构层的引线端部的金属块分别通过各自上方层间介质层中的通孔连接至各自上方相邻的半导体结构层的金属块。本发明在现有的测试结构基础上,兼顾失效分析的需求,通过在引线上添加通孔及方块金属将每个测试单元结构连接到外围电路的引线端引到样品表面,提高研磨效率和研磨成功率,从而满足最初始的电性分析,提高失效分析成功率和分析效率。

800

800

0

0

本发明公开了一种测试结构失效分析方法,第一次是通过测试垫进行电性测量缩小分析范围,第二次是通过衬垫及VC分析进一步缩小分析范围,再将缩小范围后的样品去层处理到需要观察的层次,就可以用VC观测到测试结构断点位置。采用本发明能够提高失效分析的成功率。

757

757

0

0

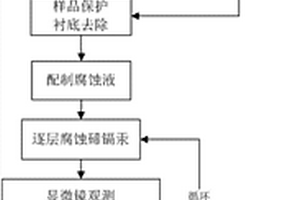

本发明公开了一种碲镉汞红外焦平面探测器的失效分析方法。先将碲镉汞红外焦平面探测器中的碲镉汞红外光敏芯片与读出电路用切割的方式进行分离,通过宝石电极基板对碲镉汞红外光敏芯片进行电流电压测试;保护不需要观测的结构,对碲镉汞红外焦平面探测器的衬底去除后露出碲镉汞表面,用配制的腐蚀液逐层腐蚀碲镉汞,观察碲镉汞结区、钝化层及倒焊等界面,与焦平面测试结果和电流电压测试结果进行对比,获取器件失效的工艺原因。采用该方法可以对成型后的碲镉汞红外焦平面探测器的性能失效进行逆向工艺分析,对碲镉汞进行逐层腐蚀逐层观测,定位失效的工艺原因,从而改进工艺,进一步提高器件的成品率。

892

892

0

0

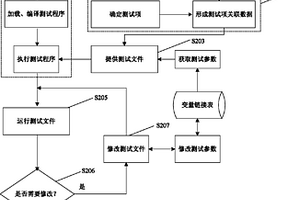

本发明提供了一种电性失效分析的测试方法,包括:提供电性失效分析中各测试项的测试项函数;根据电性失效分析的测试需求,确定电性失效分析的测试项,基于测试项形成测试项关联数据,测试项关联数据与对应的测试项函数关联;提供对应测试需求的测试文件,测试文件包括关联于测试项的测试项关联数据及对应的测试参数;运行测试文件,获取测试结果;根据测试结果和测试需求,在需修改测试文件时,调整所述测试参数。本发明还提供了一种电性失效分析的测试装置。本发明提供的技术方案无需了解测试程序即可修改测试参数并且无需反复加载和编译测试程序即可灵活改变测试流。

880

880

0

0

本发明提供了一种带失效分析标尺的电迁移测试结构,包括测试金属线、测试金属通孔、金属引线、金属线标尺及测试金属垫,所述测试金属线的端部通过所述测试金属通孔与所述金属引线的一端连接,所述金属引线的另一端与所述测试金属垫连接,所述金属线标尺形成于一至少一层金属层上,并用于定位所述测试金属通孔的至少一个目标截面。通过设计定位所述测试金属通孔不同目标截面位置的金属线标尺,实现电迁移结构失效分析切片位置的精准定位。特别是在多样品分析比较时,能够锁定每个样品的切片截面位置,通过比较各金属通孔相同横截面位置的形貌差异,为不同样品工艺差异分析提供证据,从而保证电迁移结构失效分析数据的准确性和可比性。

1170

1170

0

0

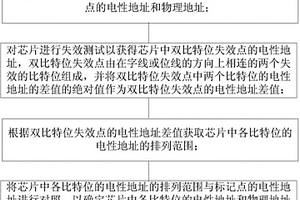

本申请公开了一种芯片的地址测试方法及芯片的失效分析方法。该芯片包括沿字线和位线的方向排列的多个比特位,该方法包括:对芯片中的部分比特位进行标记以形成标记点,并获得标记点的电性地址和物理地址;对芯片进行失效测试以获得芯片中双比特位失效点的电性地址,双比特位失效点由在字线或位线的方向上相连的两个失效的比特位组成,并将双比特位失效点中两个比特位的电性地址的差值的绝对值作为双比特位失效点的电性地址差值;根据双比特位失效点的电性地址差值获取芯片中各比特位的电性地址的排列范围;将芯片中各比特位的电性地址的排列范围与标记点的电性地址进行对照。该方法能够准确分析出芯片中物理地址和电性地址的对应关系。

1030

1030

0

0

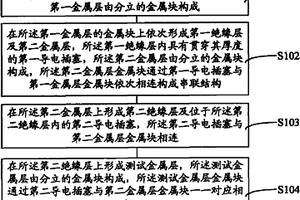

本发明提供一种失效分析结构的形成方法,包括:提供基底,并在所述基底上形成第一金属层;在所述第一金属层上依次形成第一导电插塞及第二金属层,所述第二金属层通过第一导电插塞与第一金属层依次相连构成串联结构;在所述第二金属层上形成第二绝缘层及第二导电插塞,所述第二导电插塞与第二金属层相连;在所述第二绝缘层上形成测试金属层,所述测试金属层通过第二导电插塞与第二金属层相连。本发明还提供一种失效分析结构及其失效分析方法。本发明失效分析结构和失效分析方法仅需要暴露出测试金属层,不会损害第二金属层,提高失效分析结果的准确性。

758

758

0

0

本发明涉及一种用于栅氧化层失效分析的测试结构及栅氧化层失效分析方法,所述测试结构包括含有栅氧化层的待测半导体器件,以及位于所述待测半导体器件外围的在施加偏置电压后能产生光发射的至少1个半导体器件,避免了现有技术在失效定位过程中产生的叠图偏差,达到准确定位栅氧化层的失效位置的目的。

1265

1265

0

0

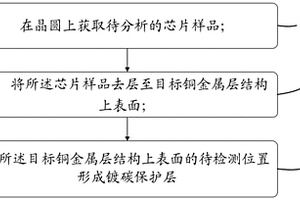

本发明提供了一种用于失效分析的样品的处理方法及失效分析方法,所述用于失效分析的样品的处理方法包括:在晶圆上获取待分析的芯片样品;将所述芯片样品去层至目标铜金属层结构上表面;在所述目标铜金属层结构上表面的待检测位置形成镀碳保护层。本发明的技术方案降低了金属表面出现铜扩散的概率,使得在失效分析过程中制备芯片样品的失败率大大降低,并且缩短了分析周期,加快了找到芯片失效关键原因的速度。

834

834

0

0

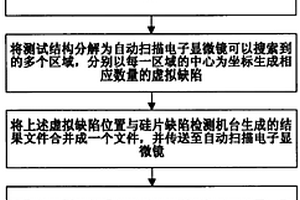

本发明公开了一种BEOL测试芯片在线失效分析的方法。本发明通过拆分特性测试的失效结构生成多个虚拟缺陷,并合成检测缺陷结果的方法,实现了自动自动扫描电子显微镜对失效位置的寻找确认和分析。本发明可以避免对硅片的破坏性分析,提高分析效率和成功率,同时实现对检测程序的实时反馈,提高程序优化的效率和准确率。本发明适用于半导体工艺中BEOL测试芯片在线失效分析方法。

1046

1046

0

0

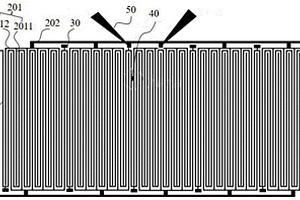

本发明提供了一种测试结构,包括蛇形金属线和两个相对交错设置的测试梳状结构,每个测试梳状结构分成至少两个子梳状结构,且每个所述测试梳状结构中的相邻两个所述子梳状结构之间具有间隔,且每个所述测试梳状结构中的至少一个所述间隔处的所述蛇形金属线的至少一个拐弯部位上引出有焊盘。即通过上述方法将所述测试结构分成了若干个小面积的测试结构,能够解决EBIRCH不能定位到超大面积结构nA级别漏电的短路点的问题;同时结合电阻比例法,以使得EBIRCH能轻易定位到超大面积结构nA级别漏电的短路点,从而找到失效的根本原因,对解决工艺问题以及促进研发进度能有很大的帮助。

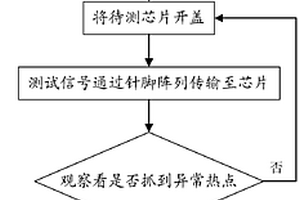

本发明提供一种针对待测芯片设计专用载板、测试设备、芯片电性失效分析的方法,所述方法包括:针对待测芯片设计专用载板,所述载板包括位于待测芯片容纳区域的焊盘阵列、用于与测试机台进行信号传输的针脚阵列,以及连接所述针脚阵列和焊盘阵列的金属连线;将待测芯片采用SMT技术贴装于所述载板上。本发明提供的芯片电性失效分析的方法和用于芯片电性失效分析的专用载板以及测试设备能够方便快捷的完成硬件准备,且能够容易的实现大管脚数目芯片测试的芯片失效分析。

907

907

0

0

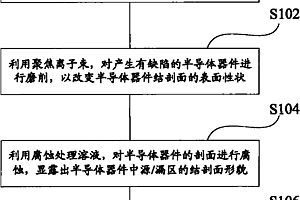

一种用于半导体器件失效分析的检测方法,包括:利用聚焦离子束,对产生有缺陷的半导体器件剖面进行磨削,以改变源/漏区的表面性状;利用腐蚀处理溶液,对所述半导体器件的剖面进行腐蚀,以显露出源/漏区的结剖面形貌;利用放大成像装置得到对应所述半导体器件的剖面的图像资料,观察所述图像资料以获取所述半导体器件所产生的缺陷的分布情况。本发明通过聚焦离子束磨削和腐蚀处理溶液腐蚀相结合,获得易于观察的半导体器件的源/漏区的结剖面形貌,提供判断器件是否失效的依据。

1236

1236

0

0

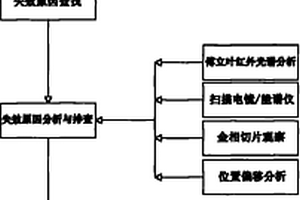

本发明属于电子产品失效分析领域。本发明提供了一种汽车车窗开关失效的检测分析方法,包括以下步骤:A、对失效的汽车车窗开关样品进行失效定位,通过外观检查和电学测试,寻找出失效的位置;B、查找失效原因;C、分析与排查失效原因:对步骤B中的可能原因依次进行验证,以确定出具体的车窗开关失效原因;D、模拟重现失效现象,验证失效机理。本发明方法步骤简单清晰,能有效找出电子产品失效的多种原因;本发明方法中使用了“穷举法”使得引起电子产品失效的原因尽可能多地被查找出来;本发明方法中通过模拟重现失效现象以提高失效原因的真实性和可靠性,极大地减少了分析出错。

1095

1095

0

0

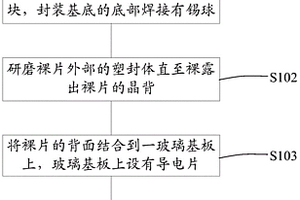

本发明公开了一种覆晶芯片失效分析方法及电性定位中检测样品的制备方法,所述制备方法包括:提供待测的覆晶芯片,包括封装基底与制备于封装基底上的裸片,裸片的外部覆盖有塑封体,裸片与封装基底之间连接有金凸块,封装基底的底部焊接有锡球;研磨裸片外部的塑封体直至裸露出裸片的晶背;将裸片的背面结合到一玻璃基板上,玻璃基板上设有导电片;用封装绑线将玻璃基板上的导电片与封装基底底部的锡球电性连接,以得到检测样品。本发明覆晶芯片失效分析检测样品的制备方法,通过研磨掉裸片的背面的塑封体,再将裸片的背面结合在玻璃基板上进行失效分析,不必腐蚀塑封体以及分离封装基底与裸片,从而避免了取裸片的过程中金凸块被腐蚀的可能性。

1145

1145

0

0

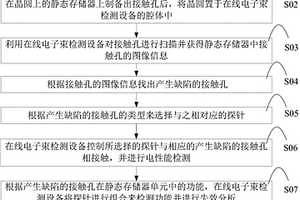

本发明提供了一种静态存储器的在线失效分析方法和在线电子束检测设备,包括:将不同类型的探针安装到在线电子束检测设备的腔体中;将晶圆置于在线电子束检测设备的腔体中;利用在线电子束检测设备对接触孔进行扫描并获得静态存储器中接触孔的图像信息;根据接触孔的图像信息找出产生缺陷的接触孔;根据产生缺陷的接触孔的类型来选择与之相对应的探针;在线电子束检测设备控制所选择的探针与相应的产生缺陷的接触孔相接触,并进行电性能检测;根据产生缺陷的接触孔在静态存储器单元中的功能,在线电子束检测设备将探针进行组合来检测功能并进行失效分析;检测到功能失效,则产生缺陷的接触孔是导致静态存储器失效的原因。

1187

1187

0

0

一种半导体失效分析结构及其形成方法、检测失效时间的方法,其中所述半导体失效分析结构包括:半导体衬底,所述半导体衬底具有待测区、第一串联区和第二串联区;位于所述半导体衬底的待测金属层、第一金属层和第二金属层;位于层间介质层内的第一导电插塞使第一金属层、第二金属层和待测金属层串联;位于所述第一串联区的若干第一电阻金属层;位于所述第二串联区的若干第二电阻金属层;位于第一串联区层间介质层内的若干第二导电插塞;位于第二串联区层间介质层内的若干第三导电插塞;所述第一导电插塞、第二导电插塞、第三导电插塞将所述待测金属层、第一金属层、第二金属层、若干第一电阻金属层和若干第二电阻金属层依次串联。

北方有色为您提供最新的上海上海有色金属失效分析技术理论与应用信息,涵盖发明专利、权利要求、说明书、技术领域、背景技术、实用新型内容及具体实施方式等有色技术内容。打造最具专业性的有色金属技术理论与应用平台!

2026年03月20日 ~ 22日

2026年03月20日 ~ 22日  2026年03月20日 ~ 22日

2026年03月20日 ~ 22日  2026年03月25日 ~ 27日

2026年03月25日 ~ 27日  2026年03月26日 ~ 28日

2026年03月26日 ~ 28日  2026年03月27日 ~ 29日

2026年03月27日 ~ 29日