全部

856

856

0

0

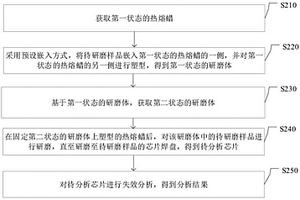

本申请提供一种芯片失效分析方法、装置、电子设备及介质。该方法在获取第一状态的热熔蜡后,第一状态为软化状态,采用预设嵌入方式,将待研磨样品嵌入第一状态的热熔蜡的一侧,并对第一状态的热熔蜡的另一侧进行塑型,得到第一状态的研磨体;研磨体中待研磨样品保持水平;基于第一状态的研磨体,获取第二状态的研磨体,第二状态为凝固状态;在固定第二状态的研磨体上塑型的热熔蜡后,对研磨体中的待研磨样品进行研磨,得到待分析芯片;对待分析芯片进行失效分析,得到分析结果。该方法提高了研磨稳定性和安全性,也提高了失效分析效率。

811

811

0

0

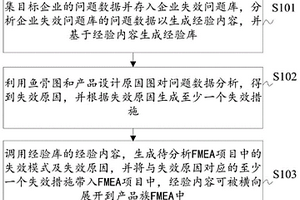

本申请公开了一种嵌入在FMEA系统中的失效分析方法及装置,方法包括:采集目标企业的问题数据并存入企业失效问题库,分析企业失效问题库的问题数据以生成经验内容,并基于经验内容生成经验库;利用鱼骨图和产品设计原因图对问题数据分析,得到失效原因,并根据失效原因生成至少一个失效措施;调用经验库的经验内容,生成待分析FMEA项目中的失效模式及失效原因,并将与失效原因对应的至少一个失效措施带入FMEA项目中,经验内容可被横向展开到产品族FMEA中。该方法解决了在做FMEA时,仅针对当前项目产品进行分析,历史经验教训难被识别应用在新项目中,导致生产问题、质量问题重复再发,造成质量损失,影响企业声誉的问题,从而可以有效防止问题再发。

835

835

0

0

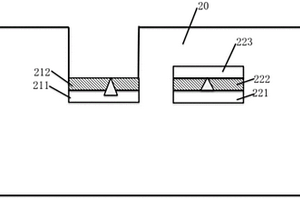

本发明提供一种半导体芯片失效分析的方法,用于对半导体芯片上的若干半导体结构进行分析,包括:提供待分析半导体芯片,所述半导体芯片中包括多个半导体结构;利用不同的分析方法分别对所述多个半导体结构进行失效分析。本发明的分析方法能够对同一半导体芯片上的不同的三明治结构采用不同的分析方法进行失效分析。

1221

1221

0

0

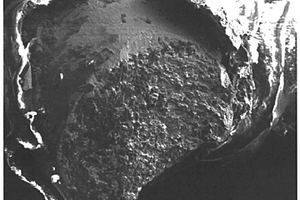

本发明提供了一种汽车电子中电动机转子漆包线断裂的失效分析方法,包括以下步骤:A、使用扫描电子显微镜对需要进行失效分析的漆包线样品断裂处的金属断口进行观察,分析可能的失效原因;B、使用X射线特征粒子能量谱仪分析漆包线样品表面的元素,通过对比漆包线导线材质设计规格书,分析出可能的失效原因;C、制作漆包线样品的金相切片样品;D、使用扫描电子显微镜观察制作好的金相切片样品,查看漆包线样品是否符合设计规范要求书的指标;E、综合以上步骤得到的结论,分析漆包线样品的失效原因及其失效机理。本发明方法步骤简单清晰易操作,有效对电动机转子漆包线断裂的失效原因进行分析,促进漆包线生产工艺的改进,提高产品质量。

857

857

0

0

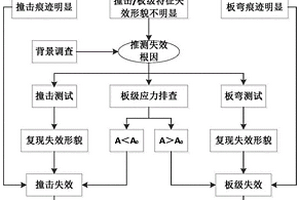

本发明涉及一种半导体器件的机械力失效分析方法,其特征在于,包括以下步骤:对失效器件分析手段,找到失效点,确定失效器件的失效形貌;将失效器件的失效形貌分三大类;对判定为第三类的失效器件做进一步分析;通过复现试验及应力分析,明确器件失效机理,分辨出碰撞力和板级应力失效;根据器件失效机理,针对性的提出碰撞力和板级应力失效的改善措施。

1167

1167

0

0

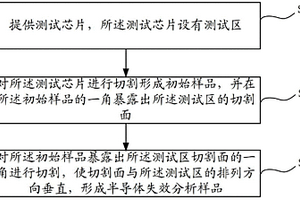

本发明提出一种制备半导体失效分析样品的方法,首先对所述测试芯片进行切割形成初始样品并在所述初始样品的一角暴露出所述测试区的切割面,其次再对所述初始样品暴露出所述测试区切割面的一角进行切割,使切割面与所述测试区的排列方向垂直,从而可以准确的测量出所述测试区的特征尺寸。

951

951

0

0

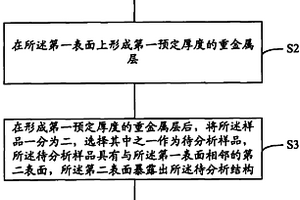

一种制备失效分析样品的方法,包括:提供样品,所述样品包括待分析结构,所述样品具有第一表面,所述第一表面暴露出待分析结构;在所述第一表面上形成第一预定厚度的重金属层;在形成第一预定厚度的重金属层后,将所述样品一分为二,选择其中之一作为待分析样品,所述待分析样品具有与所述第一表面相邻的第二表面,所述第二表面暴露出所述待分析结构;在所述待分析样品的第二表面上形成第二预定厚度的重金属层;所述重金属层的材料选自金、铂或者铬。在对该方法制备的样品进行失效分析时,基本能消除引起低介电常数材料、超低介电常数材料引起变形的因素,可以保持样品原状,提供有效的分析数据。

781

781

0

0

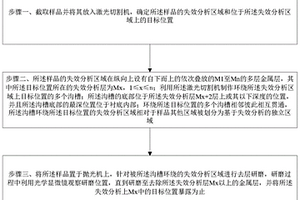

本发明提供一种失效分析去层方法,截取样品并将其放入激光切割机,确定样品的失效分析区域和目标位置;目标位置所在失效分析层为Mx;利用激光切割机制作环绕目标位置的多个沟槽;沟槽底部位于金属层Mx+2层上或其以下深度的位置;环绕目标位置的多个沟槽相邻彼此相互贯通,沟槽环绕目标位置的失效分析区域相对于样品其他区域被划分为基于失效分析的独立区域;将样品置于抛光机上,针对被沟槽环绕的失效分析区域进行去层研磨并利用光学显微镜观察研磨位置,研磨至去除失效分析层Mx以上金属层,并将失效分析上Mx中的目标位置暴露为止。本发明的失效分析去层方法在保证芯片去层精确性、有效性的同时缩短磨样时间,增强效率。

960

960

0

0

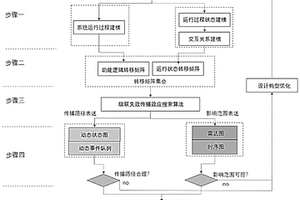

一种基于SysML模型的级联失效传播效应动态分析方法,基于SysML模型构造系统功能运行状态模型并从中提取出功能逻辑关系和运行状态级联关系,生成模型交互关系矩阵集合;再根据级联失效搜索算法从集合中的交互信息中生成失效传播链条;最后将失效传播链条整合为级联失效动态图形化结构以实现失效传播路径和影响范围的可视化。本发明能够对于复杂综合系统失效传播过程的动态描述与影响分析,达到失效传播路径和失效影响范围的可视化。

1112

1112

0

0

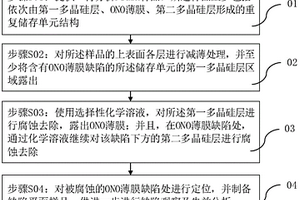

本发明公开了一种Flash产品的ONO薄膜缺陷的失效分析方法,包括对待分析Flash样品的上表面各层进行减薄处理,露出含有ONO薄膜缺陷的储存单元的第一多晶硅层区域,使用选择性化学溶液对第一多晶硅层进行腐蚀去除,露出ONO薄膜,在ONO薄膜缺陷处,通过化学溶液继续对该缺陷下方的第二多晶硅层进行腐蚀去除,对被腐蚀的ONO薄膜缺陷处进行定位,并制备缺陷平面样品,供进一步进行缺陷观察及失效分析。本发明可以更方便、准确且更精细地分析Flash产品的ONO薄膜缺陷,大大提高失效分析的效率,从而帮助迅速提高Flash产品的良率和可靠性。

1035

1035

0

0

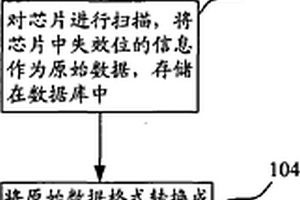

本发明提供一种芯片失效的数据分类分析方法及其装置,其方法为:确定芯片尺寸和类型;确定芯片失效模式;对芯片进行扫描,将芯片中失效位的信息作为原始数据,存储在数据库中;将原始数据格式转换成统一的标准数据格式;对所述标准数据进行分析并分类;显示分类结果。与现有的技术相比,本发明提供的芯片失效的数据分类分析方法及其装置通过确定芯片尺寸和类型;确定芯片失效模式,然后采用一维聚类算法分别将横向和纵向的失效位统计出来,再将其合并,从而大大减少统计的运算量,提高系统的性能,从而能应用于分析具有大容量的存储产品。

743

743

0

0

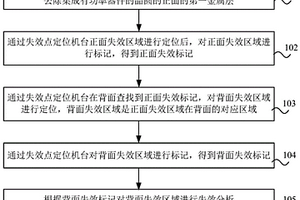

本申请公开了一种功率器件的失效分析方法,包括:去除集成有功率器件的晶圆的正面的第一金属层;通过失效点定位机台对正面失效区域进行定位后,对正面失效区域进行标记,得到正面失效标记;通过失效点定位机台在背面查找到正面失效标记,对背面失效区域进行定位,背面失效区域是正面失效区域在背面的对应区域;通过失效点定位机台对背面失效区域进行标记,得到背面失效标记;根据背面失效标记对背面失效区域进行失效分析。本申请实现了对晶圆的背面进行失效分析,提高了失效分析的准确度。

882

882

0

0

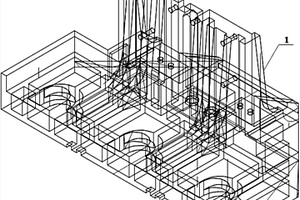

本实用新型公开了一种用于SEM/FIB失效分析的样品座,包括定位圆柱、样品存放台和固定螺丝,所示定位圆柱设置在样品存放台底部,所述样品存放台上表面开设有至少四个样品槽,每个样品槽分别对应有固定螺丝,所述固定螺丝从样品存放台侧部分别伸入到各个样品槽内。本实用新型通能同时观测多个样品,提高物性失效分析的效率;可以把多个铜工艺样品尽快放入真空室内避免被氧化污染;避免多次置换样品,保持真空值提高分辨率;改进样品固定螺丝美观且容易控制力度,避免样品被夹碎。

878

878

0

0

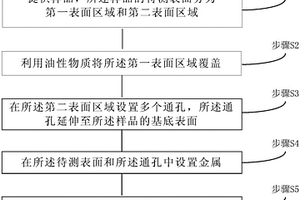

本申请提供了一种制备失效分析样品的方法。该方法包括:步骤S1.提供样品,该样品的待测表面分为第一表面区域和第二表面区域;步骤S2.利用油性物质将第一表面区域覆盖;步骤S3.在第二表面区域设置多个通孔,通孔延伸至样品的基底表面;步骤S4.在待测表面和通孔中设置金属;以及步骤S5.去除油性物质。本申请提供的方法通过在去除覆盖在第一表面区域的油性物质时同时去除附着在其上的金属,从而使第一表面区域的样品表面裸露;而第一表面区域在受到轰击时产生二次电子,与二次电子对应的正电荷被位于其周围的金属导出,由此产生的二次电子成像能够反映该处的原始表面形貌。

937

937

0

0

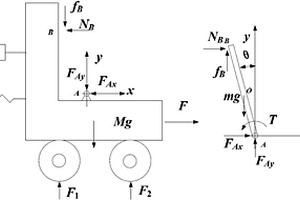

本发明公开了一种用于低压断路器振动激励失效的力学分析方法,其包括如下步骤:a)建立低压断路器的力学特性模型,包括如下操作步骤:①对振动激励下的低压断路器进行力学分析;②对经过步骤①力学分析后的低压断路器进行数学建模;③对建立的低压断路器的数学模型确定边界条件;b)分析低压断路器在振动激励下的响应特性。本发明首次提供了一种用于低压断路器振动激励失效的力学分析方法,通过建立低压断路器的数学模型、研究振动激励与低压断路器之间的力学关系,从而可掌握振动激励对低压断路器力学性能的影响,进而统计在外部环境和自身内部振动激励的影响下低压断路器的失效特性,为变载荷下载运工具的可靠性测试提供理论依据。

770

770

0

0

一种互连结构失效分析样品的制作方法,包括:对样品横截面进行物理溅射工艺;通过电子显微镜对所述样品进行测试。本发明有利于失效分析对工艺参数的准确表征。

1140

1140

0

0

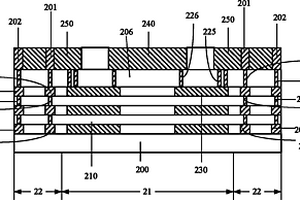

本发明提供了一种失效分析样品的制备方法,包括以下步骤:步骤S1、提供一待分析样品,所述待分析样品的一截面设置有集成电路,所述集成电路中设有一凹槽,且该集成电路除凹槽以外部分表面覆盖有一保护层;步骤S2、利用一填充材料将所述凹槽完全填充并将该凹槽所在截面完全覆盖;步骤S3、对所述待分析样品进行研磨,并对所述集成电路进行观测和分析。本发明以去除保护层时保证了良好的均匀性,样品的制备过程简单快速,且成本极低,该样品可以顺利地进行后续失效分析,同时提高了观测效率及准确率,为提高产品良率提供依据。

964

964

0

0

本发明公开了一种仿真分析低压开关端盖振动冲击失效的方法,所述方法包括如下步骤:a)建立低压开关端盖的有限元模型;b)对步骤a)所建立的有限元模型施加连续瞬态载荷;c)分析求解低压开关端盖的内部应力大小及分布;d)根据分析结果,对低压开关端盖的结构进行优化。通过本发明方法能够得到低压开关端盖在受到连续瞬态冲击载荷下,其内部的应力及分布情况,从而为避免低压开关端盖在振动冲击情况下发生失效进行结构优化和设计提供依据;本发明应用性强,对低压开关的性能监测具有重要价值。

1022

1022

0

0

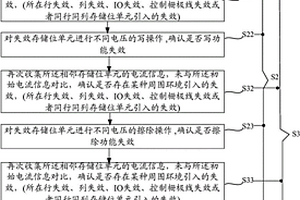

本发明提供一种共享字线的分栅式闪存的失效分析方法及系统,不仅关注失效存储位单元本身,还将与失效存储位单元共享字线的同行同列存储位单元的影响、失效存储位单元所在字线(行)、位线(列和IO接口电路)以及控制栅极线的影响等考虑在内,根据失效存储位单元的功能验证及其相邻存储位单元的电流信息前后比对,确定出失效存储位单元的失效模式是自身缺陷引起的功能失效,还是与其共享字线的同行同列存储位单元和其所在的字线、位线以及IO接口电路等周围环境缺陷引起的失效,并给出其具体失效模式,整个分析过程可自动完成,无需专业人员在场,能节约人力资源与测试机时及提高失效分析效率和结论准确性。

980

980

0

0

一种导体失效检测结构以及形成方法和检测方法,所述检测结构包括:基底,所述基底具有核心器件区和外围器件区,所述核心器件区的基底上具有分立的第一金属层和待测金属层,通过待测导电插塞相互连接;所述外围器件区的基底上具有若干重叠排布的测试焊盘和若干加载焊盘并通过贯通介质层内的测试导电插塞和加载导电插塞进行连接;在待测金属层的同一层具有焊盘金属层,所述焊盘金属层通过测试导电插塞和加载导电插塞分别与测试焊盘、加载焊盘连接,所述焊盘金属层通过至少两个顶层导电插塞与第一金属层连接。所述检测结构能够在不破坏标准焊盘结构以及不扩大设计区域面积的情况下,提高电迁移检测的准确性。

1207

1207

0

0

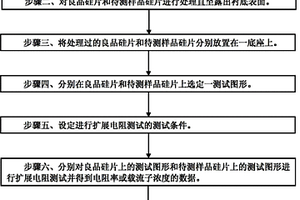

本发明公开了一种掺杂失效的分析方法,包括步骤:提供良品硅片;对良品硅片和待测样品硅片进行处理直至露出衬底表面;将良品硅片和待测样品硅片放置在底座上;在良品硅片和待测样品硅片上选定测试图形;设定进行SRP的条件;分别对良品硅片和待测样品硅片上的测试图形进行SRP并得到电阻率或载流子浓度的数据;对良品硅片和所述待测样品硅片的电阻率或载流子浓度的数据进行比较,判断待测样品硅片的掺杂是否失效,估算待测样品硅片的掺杂剂量失效大小。本发明能准确快速验证掺杂相关的失效,以及确认掺杂杂质的差异程度,能大大节省芯片失效分析的时间和确保失效分析的准确性,为明确工艺原因及提升相关产品的良率发挥重大作用。

886

886

0

0

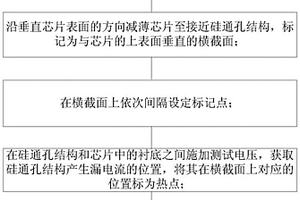

本申请公开了一种芯片的失效分析方法,该失效分析方法包括:定位芯片中产生漏电流的硅通孔结构;沿垂直芯片表面的方向研磨芯片至接近硅通孔结构,标记为与芯片的上表面垂直的横截面;在横截面上依次间隔设定标记点;在硅通孔结构和芯片中的衬底之间施加测试电压,获取硅通孔结构产生漏电流的位置,将其在横截面上对应的位置标为热点;将与热点相邻的两个标记点记为第一标记点和第二标记点,通过热点与第一标记点和第二标记点之间的深度关系定位漏电流的深度。该方法能够准确地获取芯片中漏电流的深度位置,进而有效地指导接下来的物理失效分析方法和工艺改进。同时,该方法所用的机台均为已有的传统机台,不需额外增加机台预算。

1022

1022

0

0

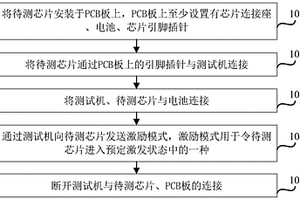

本申请公开了一种用于动态抓点的芯片失效分析的方法,涉及芯片失效分析领域。该方法包括将待测芯片安装在PCB板上,所述PCB板上至少设置有芯片连接座、电池和芯片引脚插针;将所述待测芯片通过所述PCB板上的引脚插针与测试机连接;将所述测试机、所述待测芯片与所述电池连接;通过所述测试机向所述待测芯片发送激励模式,所述激励模式用于令所述待测芯片进入预定激发状态中的一种;断开所述测试机与所述待测芯片、所述PCB板的连接;解决了目前进行动态抓点时需要搬动测试机的问题;达到了避免搬动测试机台,不限制测试机的位置,维持芯片状态方便进行动态抓点的效果。

1208

1208

0

0

本发明为一种高铁用聚氨酯弹性体防护挡板失效的综合分析方法。具体为:了解挡板的工艺参数、运行工况;对失效的挡板进行外观检查;采用三维体视显微镜等方法对失效的挡板进行更为细致的观察;采用表征方法对清洗挡板用到的清洗剂的成分进行分析;采用表征方法对失效挡板的成分、性能进行分析;采用将全新挡板简单浸泡在清洗剂中的方式对全新挡板进行实验,对浸泡结果进行收集和总结以模拟失效过程,验证实验结论;综合以上步骤,从现象到本质,从实验事实到最终结论,确定挡板失效的主要原因。本发明可以准确、快速地判断出挡板失效的原因,进而采取针对性的预防。本方法对轨道车辆领域聚氨酯防护挡板的安全使用也具有实用参考价值。

1059

1059

0

0

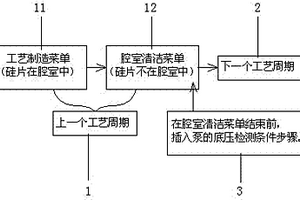

本发明公开一种新的全自动检测泵失效的方法,其中,硅片是依次传送至工艺腔室中以进行制造过程,并且泵是用于为工艺腔室抽取一定的真空度,其特征在于,在上一片硅片在工艺腔室中结束制造后,下一片硅片还没有进入工艺腔室前,增加泵的底压检测的步骤,用于检测位于工艺周期中的泵的底压状态。本发明一种新的全自动检测泵失效的方法,通过在工艺程式结束前增加设定特定的条件步骤,用来自动检测泵的底压,有效地实现泵的全自动底压检测,并防止由于泵失效产生的颗粒导致的硅片报废。从而避免人工停机人工检测所带来的资源消耗与机时的浪费,同时也解决传统的检测方法的频率太低所带来的产能风险。

1114

1114

0

0

一种用于失效分析的线路板上的元器件拆除方法,其步骤包括预处理,预热,拆除元器件,焊料整平,清洗干燥。在预处理中通过机械方法拆除非焊接连接的元器件;将线路板进行预热;在拆除元器件和焊料整平中将线路板在一定温度的高温介质中加热至焊料熔化,然后在液体介质中,拆除线路板上的元器件并将线路板表面焊盘上的焊料整平。然后将干净平整的线路板用于飞针或夹具电测试,从而找到线路板的失效网络进行失效分析。本发明与现有方法相比,大大提高了拆除效率,而且可以避免对线路板可能造成的损伤、焊锡粘连造成的线路板大量短路、以及焊盘表面不平整而不能用于线路板飞针或夹具电测试等缺陷。

1106

1106

0

0

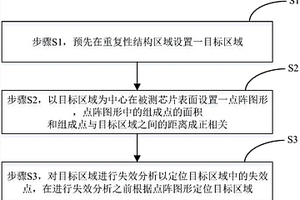

本发明公开了一种失效分析定位方法,其属于半导体领域的技术,包括:步骤S1,预先在所述重复性结构区域设置一目标区域;步骤S2,以所述目标区域为中心在所述被测芯片表面设置一点阵图形,所述点阵图形中的组成点的面积和所述组成点与所述目标区域之间的距离成正相关;步骤S3,对所述目标区域进行失效分析以定位所述目标区域中的失效点,在进行所述失效分析之前根据所述点阵图形定位所述目标区域。该技术方案的有益效果是:本发明能够减少抓取失效点的时间,以便快速的进行失效分析,提高了失效分析的效率,实现了对芯片上的重复性结构区域中的失效点的快速定位与分析。

896

896

0

0

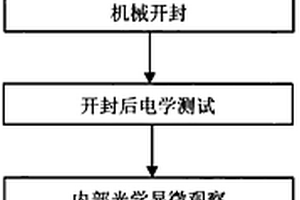

本发明提供了一种晶振失效分析的方法,包括以下步骤:A、对需要分析的晶振样品进行外观分析,寻找可能的失效原因;B、对需要分析的晶振样品进行电学测试,测出频率、等效串联电阻和最大阻抗;C、对需要分析的晶振样品进行开封,并进行电学测试;D、使用光学显微镜对开封后的晶振样品进行内部观察;E、使用扫描电子显微镜对开封后的晶振样品进行内部观察;F、综合分析上述步骤得到的结果,总结出晶振样品失效的原因。本发明有如下优点:本发明利用有限的分析仪器,在短时间内快速找到晶振元件失效的原因,分析详尽完整,为晶振的工艺生产的改进提供有效信息。

中冶有色为您提供最新的上海上海有色金属失效分析技术理论与应用信息,涵盖发明专利、权利要求、说明书、技术领域、背景技术、实用新型内容及具体实施方式等有色技术内容。打造最具专业性的有色金属技术理论与应用平台!

2025年10月23日 ~ 25日

2025年10月23日 ~ 25日  2025年10月31日 ~ 11月02日

2025年10月31日 ~ 11月02日  2025年11月07日 ~ 09日

2025年11月07日 ~ 09日  2025年11月14日 ~ 16日

2025年11月14日 ~ 16日  2025年11月14日 ~ 16日

2025年11月14日 ~ 16日